# Actions MICROELECTRONICS Co., Ltd.

Actions-micro AM8352 Datasheet

Document Number: AM8352 Datasheet Revision 1.0.0 Release date: 11/09/2021

Actions Microelectronics Co., Ltd. 701, 7floor, Golder Plaza, No.10 huayuandonglu, Haidian District, Beijing, China

## Declaration

Circuit diagrams and other information relating to products of Actions Microelectronics Company, Ltd. ("Actions-micro") are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been examined and is believed to be accurate, Actions-micro makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and disclaims any responsibility for inaccuracies. Information in this document is provided solely to enable use of Actions-micro' products. The information presented in this document does not form part of any quotation or contract for sale. Actions-micro' products, except as may expressly be provided in Actions-micro' Terms and Conditions of Sale for such products. All sales of any Actions-micro products are expressly conditional on your agreement to the terms and conditions of the most recently dated version of Actions-micro' Terms and Conditions of Sale Agreement dated before the date of your order.

The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights, copyright, trademark rights, rights in trade secrets and/or know how, or any other intellectual property rights of Actions-micro or others, however denominated, whether by express or implied representation, by estoppel, or otherwise.

Information contained herein relates solely to the Actions-micro products described herein and abrogates and supersedes, as of the release date of this publication, all previously published data and specifications relating to such products provided by Actions-micro or by any other person purporting to distribute such information. Actions-micro reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your Actions-micro sales representative to obtain the latest specifications before placing your product order. Actions-micro product may contain design defects or errors known as anomalies or errata which may cause the products functions to deviate from published specifications. Anomaly or "errata" sheets relating to currently characterized anomalies or errata are available upon request. Designers must not rely on the absence or characteristics of any features or instructions of Actions-micro' products marked "reserved" or "undefined." Actions-micro reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Actions-micro' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Actions-micro and further testing and/or modification will be fully at the risk of the customer.

ACTIONS-MICRO DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL ACTIONS-MICRO BE RELIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF ACTIONS-MICRO OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER ACTIONS-MICRO HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES OR NOT.

Copyright © Actions Microelectronics Co., Ltd 2010. All rights reserved.

### **Table of Contents**

| 1.1 Overview        | 8 |

|---------------------|---|

| 1 Introduction      | 8 |

| Declaration         | 2 |

| General Conventions |   |

| Terms and Acronyms  |   |

**Revision History**

| Version | Date       | Description    | Author    |

|---------|------------|----------------|-----------|

| 1.0.0   | 11/09/2021 | Initial Create | maweishuo |

ACTIONSM

### **Terms and Acronyms**

| Terms and Acronyms | Definition                                           |

|--------------------|------------------------------------------------------|

| CF                 | Compact Flash                                        |

| SM                 | Smart Media                                          |

| XD                 | xD picture                                           |

| SD                 | Secure Digital                                       |

| Micro SD           | Micro Secure Digital                                 |

| MS                 | Memory Stick                                         |

| MS Pro             | Memory Stick Pro                                     |

| MMC                | Multimedia Card                                      |

| SDRAM              | Synchronous Dynamic Random Access Memory             |

| MD                 | MicroDrive                                           |

| TF                 | T Flash                                              |

| LCD                | Liquid Crystal Display                               |

| ICE                | In-circuit emulation, or in-circuit emulator         |

| JTAG               | Joint Test Action Group(ANSI/ICEEE Std.11149.1-1990) |

| PQFP               | Plastic Quad Flat Package                            |

| LQFP               | Low-Profile Quad Flat Package                        |

| BGA                | Ball Grid Array                                      |

| PIP                | Picture In Picture                                   |

| ТАР                | TEST ACCESS PORT                                     |

| RGB                | Red-Green-Blue color space representation            |

| TCON               | Timing controller                                    |

|                    |                                                      |

|                    |                                                      |

ACTION

### General Conventions

| Symbol       | Description                                                                                                                                                                                                                                                                                                                       | Notes |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Note         |                                                                                                                                                                                                                                                                                                                                   |       |

| Н            | In the notes column, an H indicates the pin is hidden behind the actual physical pin listed<br>in the Alternate Functions column and is not included in the pin count. No H indicates the<br>actual pin is listed in the Signal Name column and the Alternate Functions column lists<br>the alternate signals present on the pin. |       |

| Pad GP       |                                                                                                                                                                                                                                                                                                                                   | I     |

| 1            | Pad group 1                                                                                                                                                                                                                                                                                                                       |       |

| 2            | Pad group 2                                                                                                                                                                                                                                                                                                                       |       |

| Dir/Pol (dir | ection/polarity)                                                                                                                                                                                                                                                                                                                  | l     |

| Ι            | Input                                                                                                                                                                                                                                                                                                                             |       |

| 0            | Output                                                                                                                                                                                                                                                                                                                            |       |

| В            | Bidirectional                                                                                                                                                                                                                                                                                                                     |       |

| Z            | Three state output                                                                                                                                                                                                                                                                                                                |       |

| Pad Type     | A labeled and the second se                                                                                                                                                                                                                   |       |

| А            | Analog pad                                                                                                                                                                                                                                                                                                                        |       |

| В            | Bidirectional                                                                                                                                                                                                                                                                                                                     |       |

| BS           | Bidirectional with Schmitt trigger                                                                                                                                                                                                                                                                                                |       |

| Н            | High-voltage(up to 3.0 V)tolerant digital input                                                                                                                                                                                                                                                                                   |       |

| Ι            | CMOS input                                                                                                                                                                                                                                                                                                                        |       |

| IA           | Analog input                                                                                                                                                                                                                                                                                                                      |       |

| IS           | Input with Schmitt trigger                                                                                                                                                                                                                                                                                                        |       |

| Κ            | Contains an internal weak keeper device                                                                                                                                                                                                                                                                                           |       |

| 0            | Output                                                                                                                                                                                                                                                                                                                            |       |

| OA           | Analog output                                                                                                                                                                                                                                                                                                                     |       |

| OD           | Open-drain                                                                                                                                                                                                                                                                                                                        |       |

| PD           | Contains an internal pull-down device                                                                                                                                                                                                                                                                                             |       |

| PP[NP]       | Can be programmed to non pull, pull down or pull up. The default value is no pull after reset.                                                                                                                                                                                                                                    |       |

| PP[PD]       | Can be programmed to non pull, pull down or pull up. The default value is pull down after reset.                                                                                                                                                                                                                                  |       |

| PP[PU]       | Can be programmed to non pull, pull down or pull up. The default value is pull up after reset.                                                                                                                                                                                                                                    |       |

| PU           | Contains an internal pull-up device                                                                                                                                                                                                                                                                                               |       |

| PWR          | power                                                                                                                                                                                                                                                                                                                             |       |

| Z            | High-Z output                                                                                                                                                                                                                                                                                                                     |       |

| Drive (mA)   |                                                                                                                                                                                                                                                                                                                                   |       |

| n            | Variable drive strength pins.                                                                                                                                                                                                                                                                                                     |       |

### **1** Introduction

### 1.1 Overview

The AM8352 processor from Actions-Micro is a highly integrated mix signal SoC target at multi-media applications. The AM8352 emmedded CPU is a high performance, low power 32bit RISC core with DSP instruction extension, which can run as fast as 700MHz.

The AM8352 processor features a hardwired multi-format video encoder, which supports a large variety of popular video formats including: MJPEG/H.264 at full HD resolution.

The AM8352 multi-media processor provided display solutions with the help of on chip HDMI transmitter interface.

AM8352 is also integrated with 1 USB OTG controllers, UART, I2C, SPI, etc.

CTION

#### Block Diagram

| Memory sub system      | Multi-media            | sub system              | Display sub system |

|------------------------|------------------------|-------------------------|--------------------|

| lGb DDR2<br>Controller | Video E                | OSD                     |                    |

| USB OTG                | Video Compressor       | Video Decompressor      | HDMI RX            |

| Low speed interfaces   | Multi-medi<br>Schedule | a Transfer<br>Manager   |                    |

| GPIO<br>UART/I2C/SPI   |                        |                         | Audio sub system   |

| IR TX/RX               | Core sy                | ystem                   | Audio Processor    |

|                        | RISC                   | CACHE                   | I2S in             |

| Wire/Wireless Ethernet | DMA<br>Interrupt       | BOOT ROM<br>BUS         | I2S out            |

| RGMII/MII/RMII         | Controller             | Arbiter<br>On chip SRAM |                    |

| K                      | AM8352 BLO             | CK DIAGRAM              |                    |

# 2 Feature

The AM8352 provides high level of system integration to support a wide variety of applications. The features of the AM8352 include:

#### ✓ 32BIT RISC CORE

- 32K byte instruction cache and data cache

- F/W can program from DC up to 800MHz transparently

- DSP instruction for multi-media acceleration

- Static design allows changing clock at run-time for power saving

#### ✓ VIDEO ENCODER

- Support ISO/IEC 14496-10/YU-T Rec.H.264

- Base Profile,Level 1-5.1

- Main Profile ,levels 1-5.1

- High Profile ,levels 1-5.1

- Support JPEG ITU-T Rec.T81(09/92),Baseline interleaved/JFIF

- 60 frames per second at 1920x1080 resolution for video all format

#### ✓ IMAGE/VIDEO COMPRESSOR

- Support upto 1080P Resolution

- Support 8bit YCbCr 4:2:2 & YCbYCr/RGB

- Adaptive compress ratio up to 1:6

- ✓ OSD

- 1,2 OSD bitmap data width

- 256x128 size in 2 bit or 256x256 in 1 bit

#### ✓ DISPLAY INTERFACE

- HDMI Rx support, industry standard compliance HDMI 1.3a

#### ✓ AUDIO

- I2S IN & I2S OUT interface

- Support 32 levels volume control

#### ✓ MEMORY Storage

- DDR2/3 SDRAM up to 4Gb @ 16bit up to 1066Mbps

- OTP ROM 64bit Chip ID

#### ✓ DMA CONTROLLER

- 8 physical channels and 4 bus channels

- Stride mode support

- Software configurable priority

#### ✓ Boot ROM

- On chip boot ROM with boot loader

- The system could be loaded from SPI Nor flash

#### ✓ USB 2.0 OTG

- Complies with Universal Serial Bus Specification. Revision 2.0.

- Complies with On-The-Go Supplement to the USB2.0 Specification Revision 1.0a.

- Supports point-to-point communication with one low-speed, full-speed or high-speed device in Host mode.

- Supports full-speed or high-speed in peripheral mode.

- Supports USB Mass Storage Class Bulk-Only Transport Revision 1.0 as host or device.

- Supports Electronic still picture imaging Picture Transfer Protocol (PTP)

- Supports direct print function using pict-bridge

- Supports Universal Serial Bus Device Class Definition for Printing Devices Version 1.1 as host

- Supports Universal Serial Bus Still Image Capture Device Definition Revision 1.0 as host

- Configurable/programmable size of endpoints.

- Configurable/programmable single, double, triple or quad buffering.

- Programmable type of endpoints.

- Supports high-speed high-bandwidth Isochronous and Interrupt transfer.

- Supports suspend, resume and power managements function.

- Support USB wakeup

#### ✓ OTHER INTERFACE

- UART/I2C/SPI

- 3 external interrupts

- 35 configurable GPIO shared with function pins

#### ✓ POWER

- 1.3v for core

- 3.3v/2.5v/1.8/1.5v for mac io,3.3v for others

- Core PLL, LCD PLL, Audio PLL and DDR PLL support spread spectrum

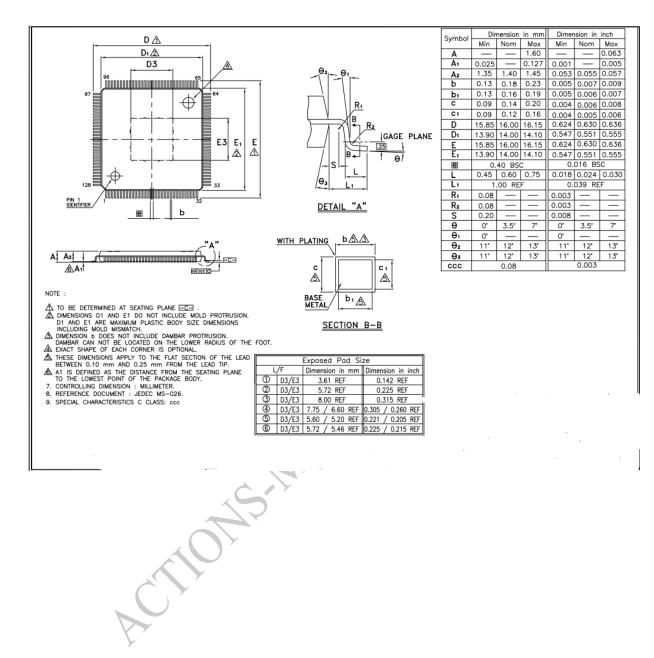

#### ✓ PACKAGE

- QFP 128pin (epad), 14x14mm

## **3** Power on Sequence

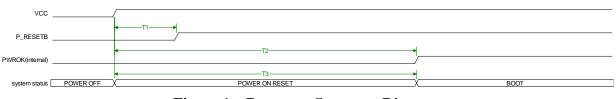

The power on sequence requirements of the AM7xxx and AM8xxx products are the same, which are shown in the following figure. VDD represents the power pins supplying power for the core. VCC represents the power pins supplying power for the general purpose pads. SVCC represents the power pins supplying power for the DDR2 or DDR3 SDRAM related pads. P\_RESETB is the asynchronous reset pin. PWROK is an internal signal. It is low during the power-on phase to reset all the registers in the chip. The system boots at the moment when PWROK turns to high.

Figure 1 Power on Sequence Diagram

Timing Requirements:

- 1.  $T1 \ge 20ms$

- 2.  $T2 \approx 128 ms$

- 3. T3 is equal to the greater one between T1 and T2.

- 4. The power on sequence of VDD/VCC/SVCC is not cared

# **4 Pin Out Specification**

Pin out table

| PIN<br>NUM | PIN NAME  | ТҮРЕ | Function  |

|------------|-----------|------|-----------|

| 1          | P_SPINSS  | В    | SPI_NSS   |

| 2          | VCC3      | PWR  | VCC3      |

| 3          | DVCC_PLL  | PWR  | AVCC_PLL2 |

| 4          | HOSCI     | А    | HOSCI     |

| 5          | HOSCO     | А    | HOSCO     |

| 6          | AVCC2     | PWR  | AVCC2     |

| 7          | VDD       | PWR  | VDD       |

| 8          | EXT_R     | А    | EXT_R     |

| 9          | AVDD33    | PWR  | AVDD33    |

| 10         | RXCN_CH   | А    | RXCN_CH   |

| 11         | RXCP_CH   | А    | RXCP_CH   |

| 12         | RX0N_CH   | А    | RX0N_CH   |

| 13         | RX0P_CH   | А    | RX0P_CH   |

| 14         | RX1N_CH   | А    | RX1N_CH   |

| 15         | RX1P_CH   | А    | RX1P_CH   |

| 16         | RX2N_CH   | А    | RX2N_CH   |

| 17         | RX2P_CH   | А    | RX2P_CH   |

| 18         | AVDD12    | PWR  | AVDD12    |

| 19         | HDMI_ON0  | A    | HDMI_ON0  |

| 20         | HDMI_OP0  | A    | HDMI_OP0  |

| 21         | AVCCPLL   | PWR  | AVCCPLL   |

| 22         | HDMI_ON1  | A    | HDMI_ON1  |

| 23         | HDMI_OP1  | А    | HDMI_OP1  |

| 24         | HDMI_ON2  | А    | HDMI_ON2  |

| 25         | HDMI_OP2  | А    | HDMI_OP2  |

| 26         | DVCCPAD   | PWR  | DVCCPAD   |

| 27         | HDMI_ON3  | А    | HDMI_ON3  |

| 28         | HDMI_OP3  | А    | HDMI_OP3  |

| 29         | CECTX     | А    | CEC_DAC   |

| 30         | CECRX     | А    | CEC_DAC   |

| 31         | P_I2C1SCL | В    | I2C1SCL   |

| 32         | P_I2C1SDA | В    | I2C1SDA   |

| 33         | VCC1      | PWR  | VCC1      |

| 34         | P_RESETB  | В    | RESETB    |

| 35         | P_UARTTX1 | В    | GPIO17    |

|    |            | <br> |                 |

|----|------------|------|-----------------|

| 36 | P_UARTRX1  | В    | GPIO18          |

| 37 | P_EXTINT0  | В    | EXTINTO         |

| 38 | P_EXTINT1  | В    | GPIO32/I2STMCLK |

| 39 | P_I2SSCK   | В    | I2SSCK/IRRX     |

| 40 | P_I2SSD    | В    | I2SSD/I2STSD    |

| 41 | P_I2SWS    | В    | I2SWS/I2STWS    |

| 42 | P_MACRVLD  | В    | RGMII_RXCTL     |

| 43 | P_MACMDIO  | В    | MACMDIO         |

| 44 | P_MACMDC   | В    | MACMDC          |

| 45 | P_MACTVLD  | В    | RGMII_TXCTL     |

| 46 | P_MACTD1   | В    | RGMII_TXD0      |

| 47 | P_MACTD0   | В    | RGMII_TXD1      |

| 48 | P_MACTCLK  | В    | RGMII_TXCLK     |

| 49 | VCC0(2.5V) | PWR  | VCC0(2.5V)      |

| 50 | P_MACRD1   | В    | RGMII_RXD1      |

| 51 | P_MACRD0   | В    | RGMII_RXD0      |

| 52 | P_MACTD2   | В    | RGMII_TXD2      |

| 53 | P_MACTD3   | В    | RGMII_TXD3      |

| 54 | P_MACRD2   | В    | RGMII_RXD2      |

| 55 | P_MACRD3   | В    | RGMII_RXD3      |

| 56 | P_MACTER   | В    | MAC_CLKO        |

| 57 | P_MACRCLK  | В    | RGMII_RXCLK     |

| 58 | VDD        | PWR  | VDD             |

| 59 | AVCC       | PWR  | AVCC            |

| 60 | VBUS0      | A    | VBUS0           |

| 61 | DM0        | A    | DM0             |

| 62 | DP0        | A    | DP0             |

| 63 | UVCC0      | PWR  | UVCC0           |

| 64 | P_DRVVBUS0 | В    | DRVVBUS0        |

| 65 | P_I2C0SCL  | В    | DDCSCL/GPIO20   |

| 66 | P_I2C0SDA  | В    | DDCSDA/GPIO21   |

| 67 | VCC2       | PWR  | VCC2            |

| 68 | P_UARTRX0  | В    | UARTRX0         |

| 69 | P_UARTTX0  | В    | UARTTX0         |

| 70 | VDD        | PWR  | VDD             |

| 71 | SVCC       | PWR  | SVCC            |

| 72 | P_DDRA12   | В    | P_DDRA12        |

| 73 | P_DDRA9    | В    | P_DDRA9         |

| 74 | P_DDRA7    | В    | P_DDRA7         |

| 75 | P_DDRA5    | В    | P_DDRA5         |

| 76 | P_DDRA3    | В    | P_DDRA3         |

| 77 | P_DDRA1    | В    | <br>P_DDRA1     |

|    | _          | ,    |                 |

| 70  |            | D   |            |

|-----|------------|-----|------------|

| 79  | P_DDRBA1   | В   | P_DDRBA1   |

| 80  | P_DDRBA0   | B   | P_DDRBA0   |

| 81  | P_DDRBA2   | В   | P_DDRBA2   |

| 82  | P_DDRWEB   | В   | P_DDRWEB   |

| 83  | VDD        | PWR | VDD        |

| 84  | SVCC       | PWR | SVCC       |

| 85  | P_DDRDQ4   | В   | P_DDRDQ4   |

| 86  | P_DDRDQ3   | В   | P_DDRDQ3   |

| 87  | P_DDRDQ1   | В   | P_DDRDQ1   |

| 88  | P_DDRDQ6   | В   | P_DDRDQ6   |

| 89  | P_DDRDQ12  | В   | P_DDRDQ12  |

| 90  | P_DDRDQ11  | В   | P_DDRDQ11  |

| 91  | P_DDRDQ9   | В   | P_DDRDQ9   |

| 92  | P_DDRDQ14  | В   | P_DDRDQ14  |

| 93  | P_DDRDM1   | В   | P_DDRDM1   |

| 94  | P_DDRDM0   | В   | P_DDRDM0   |

| 95  | VDD        | PWR | VDD        |

| 96  | SREF       | В   | SREF       |

| 97  | P_DDRDQS0  | В   | P_DDRDQS0  |

| 98  | P_DDRDQSB0 | В   | P_DDRDQSB0 |

| 99  | P_DDRDQS1  | В   | P_DDRDQS1  |

| 100 | P_DDRDQSB1 | В   | P_DDRDQSB1 |

| 101 | P_DDRDQ15  | В   | P_DDRDQ15  |

| 102 | P_DDRDQ8   | В   | P_DDRDQ8   |

| 103 | P_DDRDQ10  | B   | P_DDRDQ10  |

| 104 | P_DDRDQ13  | В   | P_DDRDQ13  |

| 105 | P_DDRDQ7   | В   | P_DDRDQ7   |

| 106 | P_DDRDQ0   | В   | P_DDRDQ0   |

| 107 | P_DDRDQ2   | В   | P_DDRDQ2   |

| 108 | P_DDRDQ5   | В   | P_DDRDQ5   |

| 109 | SVCC       | PWR | SVCCI      |

| 110 | P_DDRCLK   | В   | P_DDRCLK   |

| 111 | P_DDRCLKB  | В   | P_DDRCLKB  |

| 112 | P_DDRODT   | В   | P_DDRODT   |

| 113 | P_DDRRASB  | В   | P_DDRRASB  |

| 114 | P_DDRCSB   | В   | P_DDRCSB   |

| 115 | P_DDRCASB  | В   | P_DDRCASB  |

| 116 | VDD        | PWR | VDD        |

| 117 | P_DDRA0    | В   | P_DDRA0    |

| 118 | P_DDRA2    | В   | P_DDRA2    |

| 119 | P_DDRA4    | В   | P_DDRA4    |

| 120 | P_DDRA6    | B   | P_DDRA6    |

| ~   | +          |     |            |

| 122 | P_DDRA11  | В   | P_DDRA11     |

|-----|-----------|-----|--------------|

| 123 | SVCC      | PWR | SVCC         |

| 124 | VDD       | PWR | VDD          |

| 125 | P_IRTX    | В   | IRTX/I2STSCK |

| 126 | P_SPIMISO | В   | SPI_MISO     |

| 127 | P_SPIMOSI | В   | SPI_MOSI     |

| 128 | P_SPICLK  | В   | SPI_CLK      |

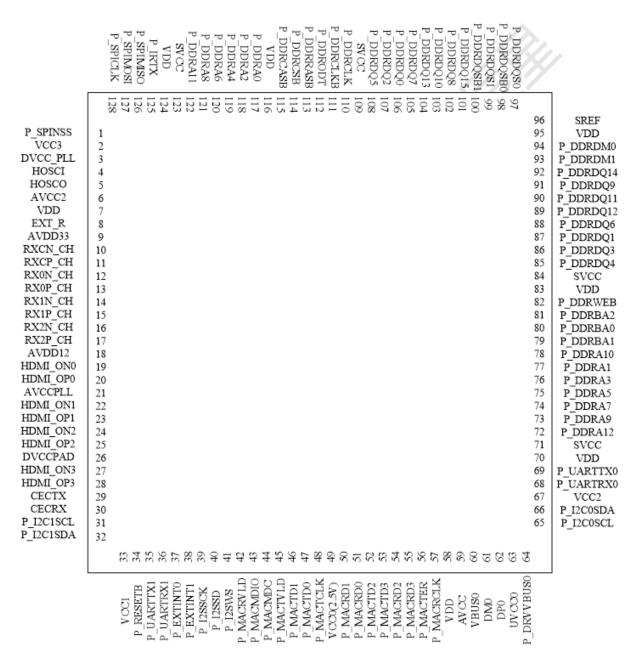

### 4.1 Pin out diagram

#### AM8352 PIN-OUT DIAGRAM

# **5** Operating Conditions

| SYMBOL          | PARAMETER             | RATING   | UNITS |

|-----------------|-----------------------|----------|-------|

| Vcc             | Power Supply (3.3V)   | 3.8      | V     |

| Vsvcc           | Power Supply (1.5V)   | 1.575    | V     |

| V <sub>dd</sub> | Power Supply (1.35V)  | 1.4      | V     |

| Vin             | Input Voltage         | -0.5~4.6 | V     |

| Vout            | Output Voltage        | -0.5~4.6 | V     |

| Тѕтс            | Storage Temperature   | 0~75     | °C    |

| То              | Operation Temperature | 0.70     | °C    |

| Тс              | (Case Surface)        | 0~70     | U     |

| Та              | Ambient Temperature   | 0~60     | °C    |

#### Absolute Maximum Ratings

**Recommended Operation Conditions**

| SYMBOL          | PARAMETER            | MIN   | ТҮР  | МАХ   | UNITS |  |

|-----------------|----------------------|-------|------|-------|-------|--|

| Vcc             | Power Supply (3.3V)  | 3.0   | 3.3  | 3.6   | V     |  |

| Vsvcc           | Power Supply (1.5V)  | 1.425 | 1.5  | 1.575 | V     |  |

| V <sub>dd</sub> | Power Supply (1.35V) | 1.3   | 1.35 | 1.4   | V     |  |

| Ta              | Ambient Temperature  | 0     | 35   | 60    | °C    |  |

|                 |                      |       |      |       |       |  |

DC Electrical Characteristics for 3.3 volts operation

#### (Under Recommended Operating Conditions and Vcc = 3.0V~3.6V, T\_j = 0 to +70 ) $\,\,^\circ\!{\rm C}$

| SYMBOL | PARAMETER                  | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|--------|----------------------------|------------|-----|-----|-----|-------|

| VIL    | Input Low Voltage          |            |     |     | 0.8 | V     |

| Vін    | Input High Voltage         |            | 2.2 |     |     | V     |

| VT-    | Schmitt Input Low Voltage  |            |     |     | 0.9 | V     |

| VT+    | Schmitt Input High Voltage |            | 1.9 |     |     | V     |

| Vol    | Output Low Voltage         | 4mA        |     |     | 0.4 | V     |

| Vон    | Output High Voltage        | 4mA        | 2.4 |     |     | V     |

# **6** Crystal Requirements

Requirements for 24MHz oscillator.

| Description                           | Specification Requirement            |

|---------------------------------------|--------------------------------------|

| Nominal Frequency                     | 24MHz                                |

| Oscillation Mode                      | Fundamental                          |

| Frequency Tolerance at 25 °C          | ±30ppm                               |

| Temperature Stability                 | $\pm$ 50ppm                          |

| Shunt Capacitance (Co)                | 7pF (max)                            |

| Load Capacitance (CL)                 | 12pF~18pF                            |

| Equivalent Series Resistance (ESR)    | 50ohm (max)                          |

| Drive Level                           | 500uW (max)                          |

| Aging (at 25℃)                        | $\pm$ 3ppm/year                      |

| Insulation Resistance                 | 10meg                                |

| Net Weight                            | This will be various. No limitation. |

| Operating Temperature Range           | -10~85°C                             |

| Storage Temperature Range             | - <b>45~125</b> ℃                    |

| equirements for 32.768KHz oscillator. |                                      |

#### Requirements for 32.768KHz oscillator.

| Description                        | Specification Requirement            |

|------------------------------------|--------------------------------------|

| Nominal Frequency                  | 32.768KHz                            |

| Oscillation Mode                   | Fundamental                          |

| Frequency Tolerance at 25 °C       | ±30ppm                               |

| Temperature Stability              | $\pm$ 50ppm                          |

| Shunt Capacitance (Co)             | 7pF (max)                            |

| Load Capacitance (CL)              | 12pF~18pF                            |

| Equivalent Series Resistance (ESR) | 50ohm (max)                          |

| Drive Level                        | 500uW (max)                          |

| Aging (at 25℃)                     | $\pm$ 3ppm/year                      |

| Insulation Resistance              | 10meg                                |

| Net Weight                         | This will be various. No limitation. |

| Operating Temperature Range        | <b>-10~85℃</b>                       |

| Storage Temperature Range          | -45~125℃                             |

### 7 Mechanical Specification